Jk Flip Flop Circuit Diagram In Logisim. The external clock is directly provided to all j k flip flops at the same time in a parallel way. Here j s and k r.

A 3 bit ripple counter using jk flip flop in the circuit shown in above figure q0 lsb will toggle for every clock pulse because jk flip flop works in toggle mode when both j and k are applied 1 1 or high input. To design jk flip flop in logisim. A theoretical schematic circuit diagram of a level triggered jk master slave flip flop is shown in fig 5 4 3.

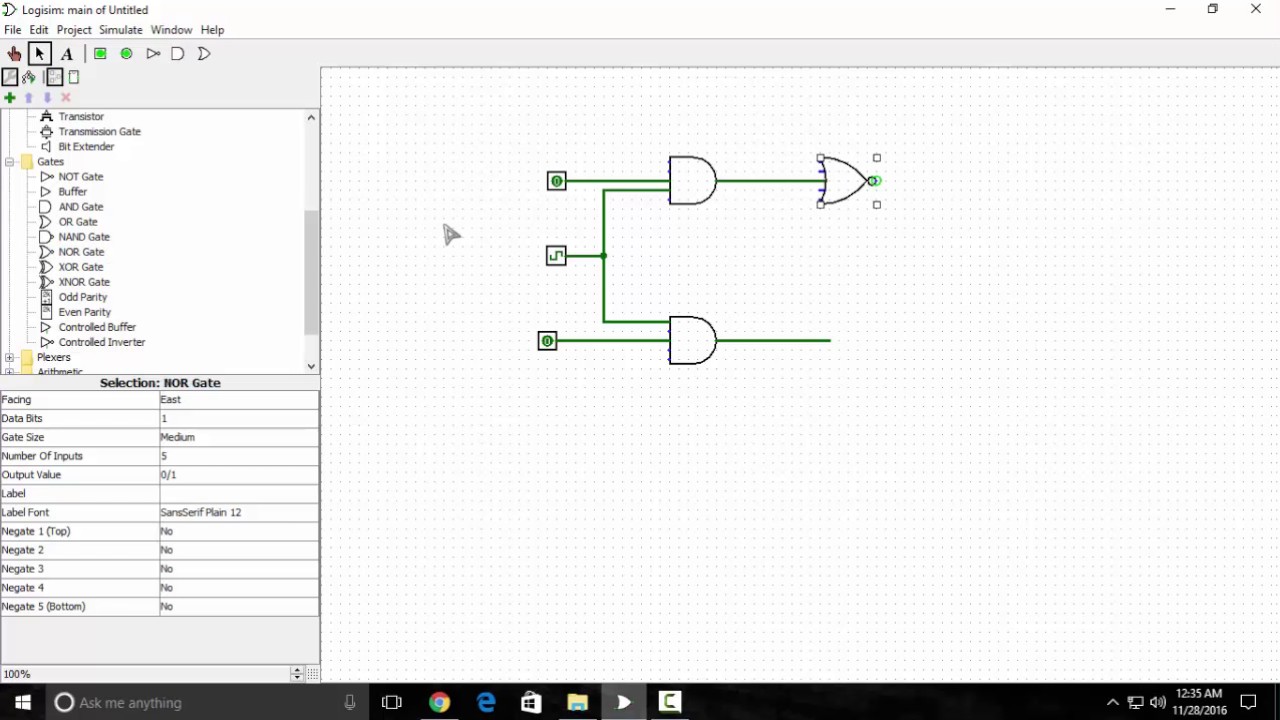

The master slave jk flip flop has two gated sr flip flops used as latches in a way that suppresses the racing or race around behavior.

The s and r inputs of the rs bistable have been replaced by the two inputs called the j and k input respectively. If we see the circuit the first flip flop ffa which is the least significant bit in this 4 bit synchronous counter is connected to a logic 1 external input via j and k pin. Outputs q and q are the usual normal and complementary outputs. The master slave jk flip flop has two gated sr flip flops used as latches in a way that suppresses the racing or race around behavior.